# $\mu$ PD780031Y, 780032Y, 780033Y, 780034Y

## 8-BIT SINGLE-CHIP MICROCONTROLLERS

#### **DESCRIPTION**

The  $\mu$ PD780031Y, 780032Y, 780033Y, and 780034Y are products based on the  $\mu$ PD780031, 780032, 780033, and 780034, with an I<sup>2</sup>C bus interface supporting multimaster added to make them suitable for application in AV equipment.

A flash memory version, the  $\mu$ PD78F0034Y which can operate in the same power supply voltage range as the mask ROM version, and various development tools, are also under development.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.

$\mu$ PD780024, 780034, 780024Y, 780034Y Subseries User's Manual : U12022E 78K/0 Series User's Manual – Instructions : U12326E

#### **FEATURES**

· Internal ROM and RAM

| Item<br>Part Number      | Program Memory<br>(Internal ROM) | Data Memory<br>(Internal High-Speed RAM) | Package                                                                  |

|--------------------------|----------------------------------|------------------------------------------|--------------------------------------------------------------------------|

| μPD780031Y<br>μPD780032Y | 8 Kbytes<br>16 Kbytes            | 512 bytes                                | 64-pin plastic shrink DIP (750 mils)     64-pin plastic QFP (14 × 14 mm) |

| μPD780033Y               | 24 Kbytes                        | 1024 bytes                               | 64-pin plastic LQFP (12 × 12 mm)                                         |

| μPD780034Y               | 32 Kbytes                        |                                          |                                                                          |

- · External memory expansion space: 64 Kbytes

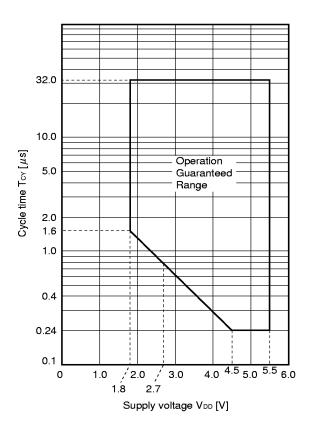

- Minimum instruction execution time: 0.24  $\mu$ s (at fx = 8.38-MHz operation)

- \*

- I/O ports: 51 (N-ch open-drain 5-V withstand voltage: 4)

- 10-bit resolution A/D converter: 8 channels (AVDD = 2.7 to 5.5 V)

- · Serial interface: 3 channels

- · Timer: 5 channels

- Power supply voltage: VDD = 1.8 to 5.5 V

## **APPLICATIONS**

Telephones, home electric appliances, pagers, AV equipment, car audios, office automation equipment, etc.

The information in this document is subject to change without notice.

Document No. U12166EJ1V0DS00 (1st edition) Date Published November 1997 N Printed in Japan The mark ★ shows major revised points.

# ORDERING INFORMATION

| Part Number                               | Package                                 |

|-------------------------------------------|-----------------------------------------|

| μPD780031YCW-×××                          | 64-pin plastic shrink DIP (750 mils)    |

| $\mu$ PD780031YGC- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $\times$ 14 mm)  |

| $\mu$ PD780031YGK- $\times$ $\times$ -8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

| $\mu$ PD780032YCW- $\times\!\!\times\!\!$ | 64-pin plastic shrink DIP (750 mils)    |

| $\mu$ PD780032YGC-×××-AB8                 | 64-pin plastic QFP (14 × 14 mm)         |

| $\mu$ PD780032YGK- $\times$ $\times$ -8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

| $\mu$ PD780033YCW- $\times\!\!\times\!\!$ | 64-pin plastic shrink DIP (750 mils)    |

| $\mu$ PD780033YGC-×××-AB8                 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

| μPD780033YGK-×××-8A8                      | 64-pin plastic LQFP (12 $\times$ 12 mm) |

| $\mu$ PD780034YCW- $\times\!\!\times\!\!$ | 64-pin plastic shrink DIP (750 mils)    |

| $\mu$ PD780034YGC- $\times$ $\times$ -AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

| μPD780034YGK-×××-8A8                      | 64-pin plastic LQFP (12 $\times$ 12 mm) |

**Remark** ××× indicates the ROM code suffix.

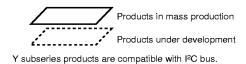

#### ★ 78K/0 SERIES PRODUCT DEVELOPMENT

These products are a further development in the 78K/0 Series. The designations appearing inside the boxes are subseries names.

Note Under planning

The major functional differences among the Y subseries are shown below.

| Subserie     |                                                             | ROM Capacity     | Configuration of Serial Interface                                                                                       | •                          | 1/0 | V <sub>DD</sub> MIN.<br>Value |

|--------------|-------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-------------------------------|

| Control      | μPD78078Y                                                   | 48 K to 60 K     |                                                                                                                         |                            | 88  | 1.8 V                         |

|              | μPD78070A                                                   | -                | 3-wire with automatic transmit/receive function 3-wire/UART                                                             | : 1 ch<br>: 1 ch           | 61  | 2.7 V                         |

|              | μPD780018AY                                                 | 48 K to 60 K     | 3-wire with automatic transmit/receive function<br>Time-division 3-wire<br>I <sup>2</sup> C bus (multimaster supported) | : 1 ch<br>: 1 ch<br>: 1 ch | 88  |                               |

|              | μPD780058Y                                                  | 24 K to 60 K     | 3-wire/2-wire/l <sup>2</sup> C<br>3-wire with automatic transmit/receive function<br>3-wire/time-division UART          | : 1 ch<br>: 1 ch<br>: 1 ch | 68  | 1.8 V                         |

|              | μPD78058FY                                                  | 48 K to 60 K     | 3-wire/2-wire/l <sup>2</sup> C                                                                                          | : 1 ch                     | 69  | 2.7 V                         |

|              | 3-wire with automatic transmit/receive function 3-wire/UART | : 1 ch<br>: 1 ch |                                                                                                                         | 2.0 V                      |     |                               |

|              | μPD780034Y                                                  | 8 K to 32 K      | UART                                                                                                                    | : 1 ch                     | 51  | 1.8 V                         |

|              | μPD780024Y                                                  |                  | 3-wire I <sup>2</sup> C bus (multimaster supported)                                                                     | : 1 ch<br>: 1 ch           |     |                               |

|              | μPD78018FY                                                  | 8 K to 60 K      | 3-wire/2-wire/I <sup>2</sup> C 3-wire with automatic transmit/receive function                                          | : 1 ch<br>: 1 ch           | 53  |                               |

|              | μPD78014Y                                                   | 8 K to 32 K      | 3-wire/2-wire/SBI/I <sup>2</sup> C<br>3-wire with automatic transmit/receive function                                   | : 1 ch<br>: 1 ch           |     | 2.7 V                         |

|              | μPD78002Y                                                   | 8 K to 16 K      | 3-wire/2-wire/SBI/I <sup>2</sup> C                                                                                      | : 1 ch                     |     |                               |

| LCD<br>drive | μPD780308Y                                                  | 48 K to 60 K     | 3-wire/2-wire/l <sup>2</sup> C<br>3-wire/time-division UART<br>3-wire                                                   | : 1 ch<br>: 1 ch<br>: 1 ch | 57  | 2.0 V                         |

|              | μPD78064Y                                                   | 16 K to 32 K     | 3-wire/2-wire/l <sup>2</sup> C<br>3-wire/UART                                                                           | : 1 ch<br>: 1 ch           | 57  |                               |

Remark The functions other than the serial interface are common to the Subseries without Y.

## **FUNCTION OVERVIEW**

| Item                            | Part Number                     | μPD780031Y                                                                                                                                                                                   | μPD780032Y                                                    | μPD780033Y                                | μPD780034Y |  |  |  |

|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|------------|--|--|--|

| Internal                        | ROM                             | 8 Kbytes                                                                                                                                                                                     | 16 Kbytes                                                     | 24 Kbytes                                 | 32 Kbytes  |  |  |  |

| memory                          | High-speed RAM                  | 512 bytes                                                                                                                                                                                    | 512 bytes 1024 bytes                                          |                                           |            |  |  |  |

| Memory space                    | ce                              | 64 Kbytes                                                                                                                                                                                    |                                                               |                                           |            |  |  |  |

| General-purp                    | oose registers                  | 8 bits × 32 registers (                                                                                                                                                                      | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)        |                                           |            |  |  |  |

| Minimum instr                   | ruction execution time          | On-chip variable fund                                                                                                                                                                        | tion of minimum instruc                                       | ction execution time                      |            |  |  |  |

|                                 | When main system clock selected | 0.24 μs/0.48 μs/0.95                                                                                                                                                                         | μs/1.91 μs/3.81 μs (at                                        | 8.38-MHz operation)                       |            |  |  |  |

|                                 | When subsystem clock selected   | 122 μs (at 32.768-kH                                                                                                                                                                         | z operation)                                                  |                                           |            |  |  |  |

| Instruction se                  | ət                              |                                                                                                                                                                                              | ts $\times$ 8 bits,16 bits $\div$ 8 bireset, test, Boolean op | '                                         |            |  |  |  |

| I/O ports                       |                                 | Total                                                                                                                                                                                        |                                                               | : 51                                      |            |  |  |  |

|                                 |                                 | CMOS input  CMOS I/O  N-ch open-drain I/O (5-V withstand voltage)  4                                                                                                                         |                                                               |                                           |            |  |  |  |

| A/D converte                    | er                              | 10-bit resolution × 8 channels     Low-voltage operation available: AVDD = 2.7 to 5.5 V                                                                                                      |                                                               |                                           |            |  |  |  |

| Serial interfa                  | ce                              | 3-wire serial I/O mode : 1 channel      UART mode : 1 channel      I <sup>2</sup> C bus mode (multimaster supported) : 1 channel                                                             |                                                               |                                           |            |  |  |  |

| Timer                           |                                 | 16-bit timer/event co     8-bit timer/event co     Watch timer     Watchdog timer                                                                                                            | unter : 2<br>: 1                                              | channel<br>channels<br>channel<br>channel |            |  |  |  |

| Timer output                    |                                 | 3 (8-bit PWM output                                                                                                                                                                          | capable: 2)                                                   |                                           |            |  |  |  |

| Clock output                    |                                 | 65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.10 MHz, 4.19 MHz, 8.38 MHz     (at 8.38-MHz operation with main system clock)     32.768 kHz (at 32.768-kHz operation with subsystem clock) |                                                               |                                           |            |  |  |  |

| Buzzer outpu                    | ut                              | 1.02 kHz, 2.05 kHz, 4.10 kHz, 8.19 kHz (at 8.38-MHz operation with main system clock)                                                                                                        |                                                               |                                           |            |  |  |  |

| Vectored Maskable               |                                 | Internal: 13, external: 5                                                                                                                                                                    |                                                               |                                           |            |  |  |  |

| interrupt Non-maskable Software |                                 | Internal: 1                                                                                                                                                                                  |                                                               |                                           |            |  |  |  |

|                                 |                                 | 1                                                                                                                                                                                            |                                                               |                                           |            |  |  |  |

| Power supply voltage            |                                 | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                               |                                                               |                                           |            |  |  |  |

| Operating ambient temperature   |                                 | T <sub>A</sub> = -40 to +85°C                                                                                                                                                                |                                                               |                                           |            |  |  |  |

| Package                         |                                 | 64-pin plastic shrink DIP (750 mils)     64-pin plastic QFP (14 × 14 mm)     64-pin plastic LQFP (12 × 12 mm)                                                                                |                                                               |                                           |            |  |  |  |

$\star$

# **CONTENTS**

| • | 1. PIN  | I CONFIGURATION (Top View)                                 | 7  |

|---|---------|------------------------------------------------------------|----|

| 2 | 2. BL   | OCK DIAGRAM                                                | 10 |

| ; | 3. PIN  | I FUNCTIONS                                                | 11 |

|   | 3.1     | Port Pins                                                  | 11 |

|   | 3.2     | Non-port Pins                                              | 12 |

|   | 3.3     | Pin I/O Circuits and Recommended Connection of Unused Pins | 14 |

| 4 | 4. ME   | MORY SPACE                                                 | 16 |

| į | 5. PER  | RIPHERAL HARDWARE FUNCTION FEATURES                        | 17 |

|   | 5.1     | Ports                                                      | 17 |

|   | 5.2     | Clock Generator                                            |    |

|   | 5.3     | Timer/Counter                                              |    |

|   | 5.4     | Clock Output/Buzzer Output Control Circuit                 |    |

|   | 5.5     | A/D Converter                                              |    |

|   | 5.6     | Serial Interface                                           | 25 |

| ( | 6. INT  | ERRUPT FUNCTIONS                                           | 28 |

| - | 7. EX   | TERNAL DEVICE EXPANSION FUNCTIONS                          | 31 |

| 8 | B. STA  | ANDBY FUNCTIONS                                            | 31 |

| ( | 9. RES  | SET FUNCTIONS                                              | 31 |

| • | 10. INS | STRUCTION SET                                              | 32 |

|   | 11. ELE | ECTRICAL SPECIFICATIONS                                    | 34 |

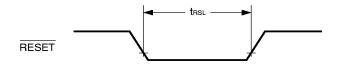

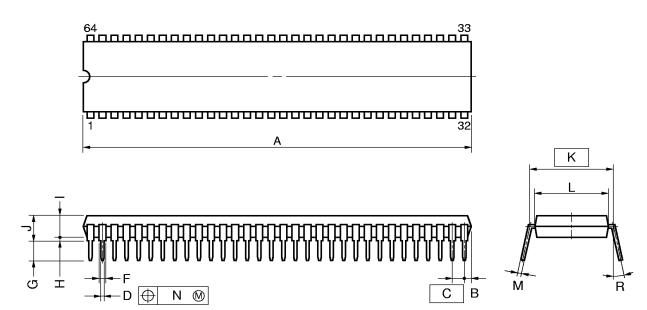

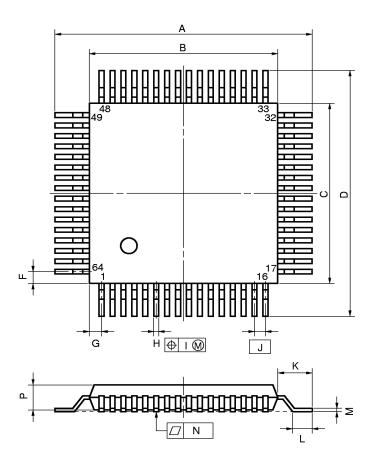

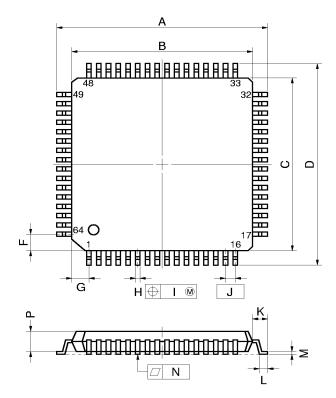

|   | 12. PA  | CKAGE DRAWINGS                                             | 55 |

| 4 | APPEN   | IDIX A. DEVELOPMENT TOOLS                                  | 58 |

| 4 | APPEN   | IDIX B. RELATED DOCUMENTS                                  | 61 |

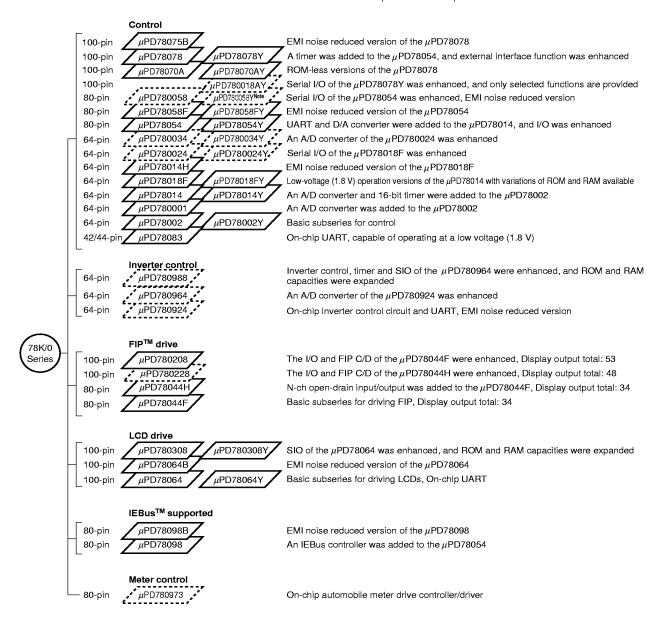

## 1. PIN CONFIGURATION (Top View)

• 64-pin plastic shrink DIP (750 mils)

μPD780031YCW-xxx, 780032YCW-xxx, 780033YCW-xxx, 780034YCW-xxx

- Cautions 1. Connect the IC (Internally Connected) pin directly to Vsso or Vss1.

- 2. Connect the AVss pin to Vsso.

**Remark** When the  $\mu$ PD780031Y, 780032Y, 780033Y, and 780034Y are used in applications where the noise generated inside the microcontroller needs to be reduced, the implementation of noise reduction measures, such as supplying voltage to VDD0 and VDD1 individually and connecting Vss0 and Vss1 to different ground lines, is recommended.

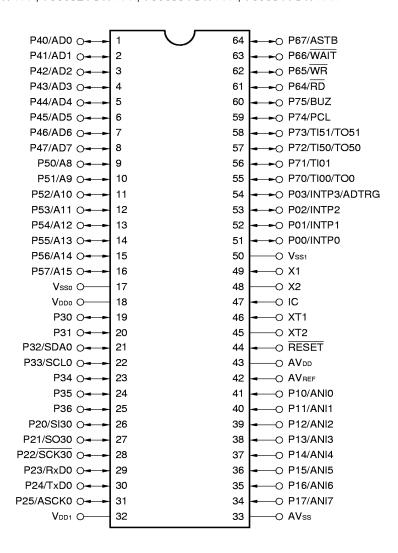

- 64-pin plastic QFP (14 × 14 mm)

μPD780031YGC-xxx-AB8, 780032YGC-xxx-AB8, 780033YGC-xxx-AB8, 780034YGC-xxx-AB8

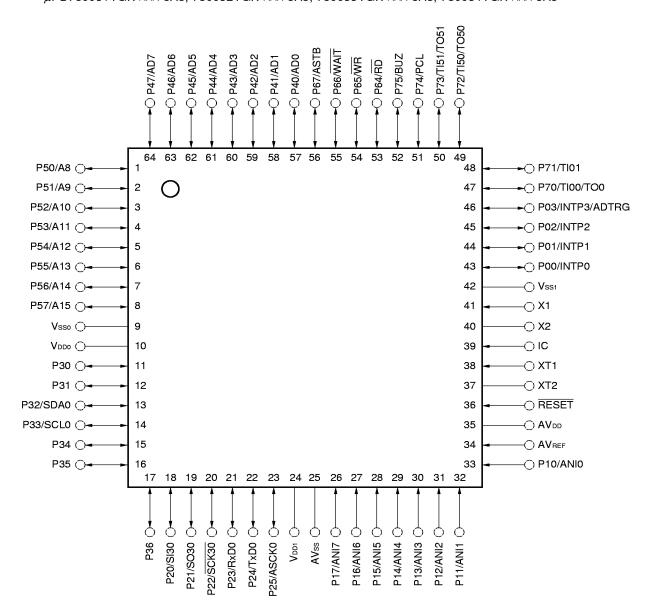

- 64-pin plastic LQFP (12 × 12 mm)  $\mu PD780031YGK-xxx-8A8, 780032YGK-xxx-8A8, 780033YGK-xxx-8A8, 780034YGK-xxx-8A8$

- ★ Cautions 1. Connect the IC (Internally Connected) pin directly to Vss₀ or Vss₁.

- 2. Connect the AVss pin to Vsso.

Remark When the  $\mu$ PD780031Y, 780032Y, 780033Y, and 780034Y are used in applications where the noise generated inside the microcontroller needs to be reduced, the implementation of noise reduction measures, such as supplying voltage to VDD0 and VDD1 individually and connecting Vss0 and Vss1 to different ground lines, is recommended.

A8 to A15 : Address Bus P70 to P75 : Port 7

AD0 to AD7 : Address/Data Bus PCL : Programmable Clock

ASCK0 : Asynchronous Serial Clock RxD0 : Receive Data

ASTB : Address Strobe SCK30 : Serial Clock

AVDD : Analog Power Supply SCL0 : Serial Clock

**AV**REF : Analog Reference Voltage SDA0 : Serial Data **AV**ss : Analog Ground SI30 : Serial Input BUZ : Buzzer Clock **SO30** : Serial Output IC : Internally Connected TI00, TI01, TI50, TI51 : Timer Input : Interrupt from Peripherals TO0, TO50, TO51 INTP0 to INTP3 : Timer Output P00 to P03 : Port 0 TxD0 : Transmit Data

P00 to P03

: Port 0

TxD0

: Transmit Data

P10 to P17

: Port 1

VDD0, VDD1

: Power Supply

P20 to P25

: Port 2

Vsso, Vss1

: Ground

P30 to P36

: Port 3

WAIT

: Wait

P40 to P47 : Port 4  $\overline{\text{WR}}$  : Write Strobe

P50 to P57 : Port 5 X1, X2 : Crystal (Main System Clock)

P64 to P67 : Port 6 XT1, XT2 : Crystal (Subsystem Clock)

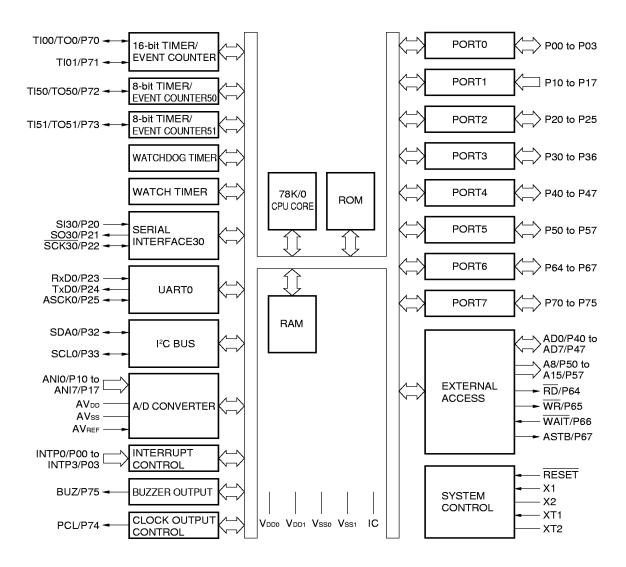

## 2. BLOCK DIAGRAM

Remark The internal ROM and RAM capacities depend on the product.

## 3. PIN FUNCTIONS

# 3.1 Port Pins (1/2)

| Pin Name   | I/O   |                                                                                                                                                                                                                                        | Function                                                       | After<br>Reset | Alternate<br>Function |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|-----------------------|

| P00        | 1/0   | Port 0                                                                                                                                                                                                                                 |                                                                | Input          | INTP0                 |

| P01        |       | 4-bit input/output port.                                                                                                                                                                                                               |                                                                | ·              | INTP1                 |

| P02        |       | Input/output can be specified bit                                                                                                                                                                                                      | -wise.<br>n-chip pull-up resistor can be connected by          |                | INTP2                 |

| P03        |       | software.                                                                                                                                                                                                                              | in emp pair up recipier can be confidence by                   |                | INTP3/ADTRG           |

| P10 to P17 | Input | Port 1<br>8-bit input only port.                                                                                                                                                                                                       |                                                                | Input          | ANI0 to ANI7          |

| P20        | 1/0   | Port 2                                                                                                                                                                                                                                 |                                                                | Input          | SI30                  |

| P21        |       | 6-bit input/output port.                                                                                                                                                                                                               |                                                                |                | SO30                  |

| P22        |       | Input/output can be specified bit When used as an input port, an o                                                                                                                                                                     | -wise.<br>on-chip pull-up resistor can be connected by         |                | SCK30                 |

| P23        |       | software.                                                                                                                                                                                                                              |                                                                |                | RxD0                  |

| P24        |       |                                                                                                                                                                                                                                        |                                                                |                | TxD0                  |

| P25        |       |                                                                                                                                                                                                                                        |                                                                |                | ASCK0                 |

| P30        | 1/0   | Port 3                                                                                                                                                                                                                                 | N-ch open-drain input/output port.                             | Input          | _                     |

| P31        |       | 7-bit input/output port.                                                                                                                                                                                                               | P30 and P31 on-chip pull-up resistors                          |                |                       |

| P32        |       | Input/output can be specified bit-wise.                                                                                                                                                                                                | can be specified by mask option.  LEDs can be driven directly. |                | SDA0                  |

| P33        |       |                                                                                                                                                                                                                                        |                                                                |                | SCL0                  |

| P34        |       |                                                                                                                                                                                                                                        | When used as an input port, an on-chip                         |                | _                     |

| P35        |       |                                                                                                                                                                                                                                        | pull-up resistor can be connected by                           |                |                       |

| P36        |       |                                                                                                                                                                                                                                        | software.                                                      |                |                       |

| P40 to P47 | 1/0   | Port 4 8-bit input/output port. Input/output can be specified bit-wise. When used as an input port, an on-chip pull-up resistor can be connected by software. Interrupt request flag (KRIF) is set to 1 by the falling edge detection. |                                                                | Input          | AD0 to AD7            |

| P50 to P57 | I/O   | Port 5 8-bit input/output port. LEDs can be driven directly. Input/output can be specified bit-wise. When used as an input port, an on-chip pull-up resistor can be connected by software.                                             |                                                                | Input          | A8 to A15             |

| P64        | 1/0   | Port 6                                                                                                                                                                                                                                 |                                                                |                | RD                    |

| P65        |       | 4-bit input/output port.                                                                                                                                                                                                               |                                                                |                | WR                    |

| P66        |       | Input/output can be specified bit-wise.  When used as an input port, an on-chip pull-up resistor can be connected by                                                                                                                   |                                                                |                | WAIT                  |

| P67        |       | software.                                                                                                                                                                                                                              |                                                                |                | ASTB                  |

# 3.1 Port Pins (2/2)

| Pin Name | I/O | Function                                                                                                             | After<br>Reset | Alternate<br>Function |

|----------|-----|----------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|

| P70      | 1/0 | Port 7                                                                                                               | Input          | TI00/TO0              |

| P71      |     | 6-bit input/output port.                                                                                             |                | TI01                  |

| P72      |     | Input/output can be specified bit-wise.  When used as an input port, an on-chip pull-up resistor can be connected by |                | TI50/TO50             |

| P73      |     | software.                                                                                                            |                | TI51/TO51             |

| P74      |     |                                                                                                                      |                | PCL                   |

| P75      |     |                                                                                                                      |                | BUZ                   |

# 3.2 Non-port Pins (1/2)

| Pin Name   | I/O    | Function                                                                                                                   | After<br>Reset | Alternate<br>Function |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|

| INTP0      | Input  | External interrupt request input for which the valid edge (rising edge,                                                    | Input          | P00                   |

| INTP1      |        | falling edge, or both rising edge and falling edge) can be specified.                                                      |                | P01                   |

| INTP2      |        |                                                                                                                            |                | P02                   |

| INTP3      |        |                                                                                                                            |                | P03/ADTRG             |

| SI30       | Input  | Serial interface serial data input.                                                                                        | Input          | P20                   |

| SO30       | Output | Serial interface serial data output.                                                                                       | Input          | P21                   |

| SDA0       | 1/0    | Serial interface serial data input/output.                                                                                 | Input          | P32                   |

| SCK30      | 1/0    | Serial interface serial clock input/output.                                                                                | Input          | P22                   |

| SCL0       |        |                                                                                                                            |                | P33                   |

| RxD0       | Input  | Serial data input for asynchronous serial interface.                                                                       | Input          | P23                   |

| TxD0       | Output | Serial data output for asynchronous serial interface.                                                                      | Input          | P24                   |

| ASCK0      | Input  | Serial clock input for asynchronous serial interface.                                                                      | Input          | P25                   |

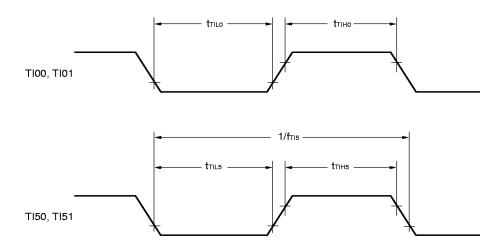

| T100       | Input  | External count clock input to 16-bit timer (TM0).  Capture trigger input to capture register (CR01) of 16-bit timer (TM0). | Input          | P70/TO0               |

| TI01       |        | Capture trigger input to capture register (CR00) of 16-bit timer (TM0).                                                    |                | P71                   |

| TI50       |        | External count clock input to 8-bit timer (TM50).                                                                          |                | P72/TO50              |

| TI51       |        | External count clock input to 8-bit timer (TM51).                                                                          |                | P73/TO51              |

| TO0        | Output | 16-bit timer (TM0) output.                                                                                                 | Input          | P70/TI00              |

| TO50       |        | 8-bit timer (TM50) output (shared with 8-bit PWM output).                                                                  | Input          | P72/TI50              |

| TO51       |        | 8-bit timer (TM51) output (shared with 8-bit PWM output).                                                                  |                | P73/TI51              |

| PCL        | Output | Clock output (for trimming of main system clock and subsystem clock).                                                      | Input          | P74                   |

| BUZ        | Output | Buzzer output.                                                                                                             | Input          | P75                   |

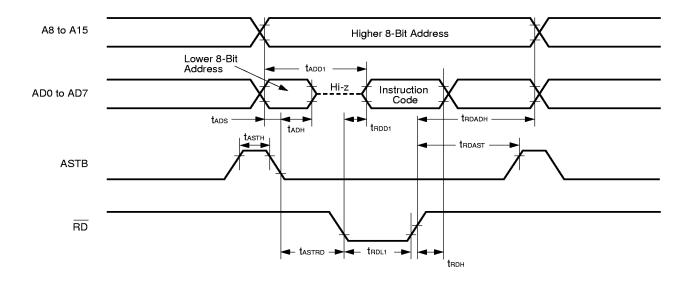

| AD0 to AD7 | I/O    | Lower address/data bus for extending memory externally.                                                                    | Input          | P40 to P47            |

| A8 to A15  | Output | Higher address bus for extending memory externally.                                                                        | Input          | P50 to P57            |

| RD         | Output | Strobe signal output for read operation of external memory.                                                                | Input          | P64                   |

| WR         |        | Strobe signal output for write operation of external memory.                                                               |                | P65                   |

| WAIT       | Input  | Inserting wait for accessing external memory.                                                                              | Input          | P66                   |

| ASTB       | Output | Strobe output which externally latches address information output to port 4 and port 5 to access external memory.          | Input          | P67                   |

# 3.2 Non-port Pins (2/2)

| Pin Name         | I/O   | Function                                                                           | After<br>Reset | Alternate<br>Function |

|------------------|-------|------------------------------------------------------------------------------------|----------------|-----------------------|

| ANI0 to ANI7     | Input | A/D converter analog input.                                                        | Input          | P10 to P17            |

| ADTRG            | Input | A/D converter trigger signal input.                                                | Input          | P03/INTP3             |

| AVREF            | Input | A/D converter reference voltage input.                                             | _              | _                     |

| AVDD             | _     | A/D converter analog power supply. Set the same potential as that of VDDD or VDD1. | _              | _                     |

| AVss             | _     | A/D converter ground potential. Set the same potential as that of Vsso or Vss1.    | _              | _                     |

| RESET            | Input | System reset input.                                                                | _              | _                     |

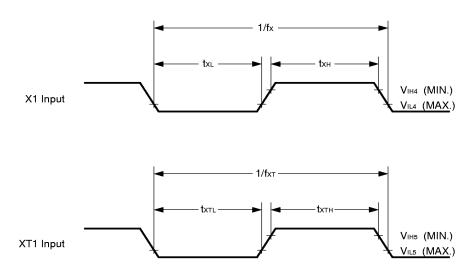

| X1               | Input | Connecting crystal resonator for main system clock oscillation.                    | _              | _                     |

| X2               | _     |                                                                                    | _              | _                     |

| XT1              | Input | Connecting crystal resonator for subsystem clock oscillation.                      | _              | _                     |

| XT2              | _     |                                                                                    | _              | _                     |

| V <sub>DD0</sub> | _     | Positive power supply for ports.                                                   | _              | _                     |

| Vsso             | _     | Ground potential of ports.                                                         | _              | _                     |

| V <sub>DD1</sub> | _     | Positive power supply (except ports).                                              | _              | _                     |

| V <sub>SS1</sub> | _     | Ground potential (except ports).                                                   | _              | _                     |

| IC               | _     | Internally connected. Connect directly to Vsso or Vss1.                            | _              | _                     |

\*

## 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 3-1. For the input/output circuit configuration of each type, see Figure 3-1.

Table 3-1. Input/Output Circuit Type of Each Pin

|   | Pin Name             | Input/output<br>Circuit Type | 1/0          | Recommended Connection when not Used                  |

|---|----------------------|------------------------------|--------------|-------------------------------------------------------|

|   | P00/INTP0            | 8-C                          | Input        | Independently connect to Vsso via a resistor.         |

|   | P01/INTP1            |                              |              |                                                       |

|   | P02/INTP2            |                              |              |                                                       |

|   | P03/INTP3            |                              |              |                                                       |

|   | P10/ANI0 to P17/ANI7 | 25                           | Input        | Independently connect to VDDO or VSSO via a resistor. |

|   | P20/SI30             | 8-C                          | Input/output |                                                       |

|   | P21/SO30             | 5-H                          |              |                                                       |

|   | P22/SCK30            | 8-C                          |              |                                                       |

|   | P23/RxD0             |                              |              |                                                       |

|   | P24/TxD0             | 5-H                          |              |                                                       |

|   | P25/ASCK0            | 8-C                          |              |                                                       |

|   | P30, P31             | 13-Q                         | Input/output | Independently connect to VDDD via a resistor.         |

| * | P32/SDA0             | 13-R                         |              |                                                       |

| * | P33/SCL0             |                              |              |                                                       |

|   | P34                  | 8-C                          |              | Independently connect to VDDD or VSSD via a resistor. |

|   | P35                  | 5-H                          |              |                                                       |

|   | P36                  | 8-C                          |              |                                                       |

|   | P40/AD0 to P47/AD7   | 5-H                          | Input/output | Independently connect to VDDD via a resistor.         |

|   | P50/A8 to P57/A15    |                              | Input/output | Independently connect to VDDD or VSSD via a resistor. |

|   | P64/RD               |                              | Input/output |                                                       |

|   | P65/WR               |                              |              |                                                       |

|   | P66/WAIT             |                              |              |                                                       |

|   | P67/ASTB             |                              |              |                                                       |

|   | P70/TI00/TO0         | 8-C                          |              |                                                       |

|   | P71/TI01             |                              |              |                                                       |

|   | P72/TI50/TO50        |                              |              |                                                       |

|   | P73/TI51/TO51        |                              |              |                                                       |

|   | P74/PCL              | 5-H                          |              |                                                       |

|   | P75/BUZ              |                              |              |                                                       |

|   | RESET                | 2                            | Input        | _                                                     |

|   | XT1                  | 16                           |              | Connect to VDDD.                                      |

|   | XT2                  |                              | _            | Leave open.                                           |

|   | AVDD                 |                              |              | Connect to VDD0.                                      |

| * | AVREF                | _                            |              | Connect to Vsso.                                      |

| * | AVss                 | _                            |              |                                                       |

| * | IC                   |                              |              | Connect directly to Vsso or Vss1.                     |

TYPE 2 TYPE 13-R★ O IN/OUT data output disable INO Schmitt-Triggered Input with Hysteresis Characteristics TYPE 5-H TYPE 16 feedback pullup cut-off enable  $V_{\underline{D}\underline{D}0}$ P-ch data P-ch O IN/OUT output - N-ch disable XT1 XT2 input enable TYPE 8-C TYPE 25 P-ch pullup Comparator enable  $V_{\text{DD0}}$ data P-ch Vsso O IN VREF (threshold voltage) O IN/OUT output - N-ch input disable ‴ Vsso enable TYPE 13-Q V<sub>DD0</sub> (Mask Option) O IN/OUT data output disable input enable

Figure 3-1. Pin Input/Output Circuits

### 4. MEMORY SPACE

Figure 4-1 shows the memory map of the  $\mu$ PD780031Y, 780032Y, 780033Y, and 780034Y.

**FFFFH** Special Function Registers (SFR) 256 × 8 bits FF00H **FEFFH** General Registers  $32 \times 8$  bits **FEE0H FEDFH** Internal High-Speed RAM<sup>Note</sup> mmmmH mmmmH - 1 nnnnH **Data Memory** Use Prohibited Program Area Space 1000H **OFFFH CALLF Entry Area** F800H 0800H F7FFH 07FFH Program Area External Memory Program Memory 0080H 007FH Space nnnnH + 1 **CALLT Table Area** nnnnH 0040H 003FH Internal ROM<sup>Note</sup> Vector Table Area 0000H 0000H

Figure 4-1. Memory Map

**Note** The internal ROM capacity and internal high-speed RAM capacity depend on the products (see the following table).

| Part Number | Internal ROM Last Address<br>nnnnH | Internal High-Speed RAM Start Address mmmmH |

|-------------|------------------------------------|---------------------------------------------|

| μPD780031Y  | 1FFFH                              | FD00H                                       |

| μPD780032Y  | 3FFFH                              |                                             |

| μPD780033Y  | 5FFFH                              | FB00H                                       |

| μPD780034Y  | 7FFFH                              |                                             |

## 5. PERIPHERAL HARDWARE FUNCTION FEATURES

## 5.1 Ports

The following 3 types of I/O ports are available.

CMOS input (Port 1) : 8

CMOS input/output (Port 0, Port 2 to Port 7) : 39

N-channel open-drain input/output (P30 to P33) : 4

Total : 51

Table 5-1. Port Functions

| Name                                                                                                                                                                              | Pin Name   | Function                                                                                                                                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port 0                                                                                                                                                                            | P00 to P03 | o P03 Input/output port pins. Input/output specifiable bit-wise.  When used as input port pins, on-chip pull-up resistor can be connected by software.                                                          |  |

| Port 1                                                                                                                                                                            | P10 to P17 | Input-only port pins.                                                                                                                                                                                           |  |

| Port 2                                                                                                                                                                            | P20 to P25 | Input/output port pins. Input/output specifiable bit-wise. When used as input port pins, on-chip pull-up resistor can be connected by software.                                                                 |  |

| Port 3 P30 to P33 N-ch open-drain input/output port pins. Input/output specifiable bit-wis On-chip pull-up resistor can be connected by mask option. LEDs can be driven directly. |            | , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                           |  |

|                                                                                                                                                                                   | P34 to P36 | Input/output port pins. Input/output specifiable bit-wise. When used as input port pins, on-chip pull-up resistor can be connected by software.                                                                 |  |

| Port 4                                                                                                                                                                            | P40 to P47 | Input/output port pins. Input/output specifiable bit-wise.  When used as input port pins, on-chip pull-up resistor can be connected by software.  Test input flag (KRIF) is set to 1 by falling edge detection. |  |

| Port 5                                                                                                                                                                            | P50 to P57 | Input/output port pins. Input/output specifiable bit-wise.  When used as input port pins, on-chip pull-up resistor can be connected by software.  LEDs can be driven directly.                                  |  |

| Port 6                                                                                                                                                                            | P64 to P67 | Input/output port pins. Input/output specifiable bit-wise. When used as input port pins, on-chip pull-up resistor can be connected by software.                                                                 |  |

| Port 7                                                                                                                                                                            | P70 to P75 | Input/output port pins. Input/output specifiable bit-wise. When used as input port pins, on-chip pull-up resistor can be connected by software.                                                                 |  |

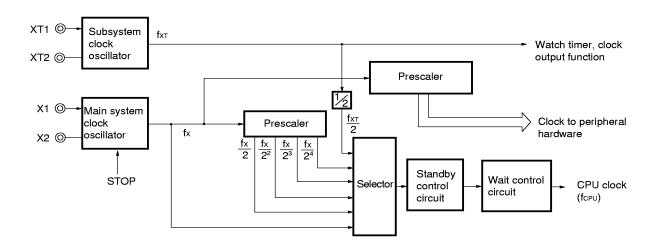

#### 5.2 Clock Generator

A system clock generator is incorporated.

Also, the variation of the minimum instruction execution time is available.

- 0.24  $\mu$ s/0.48  $\mu$ s/0.95  $\mu$ s/1.91  $\mu$ s/3.81  $\mu$ s (at 8.38-MHz operation with main system clock)

- 122 μs (at 32.768-kHz operation with subsystem clock)

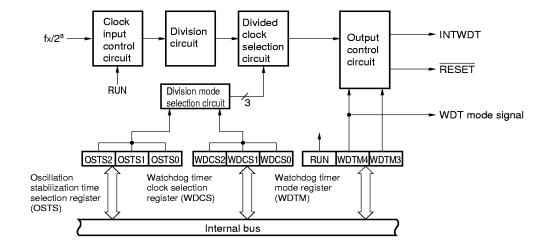

Figure 5-1. Block Diagram of Clock Generator

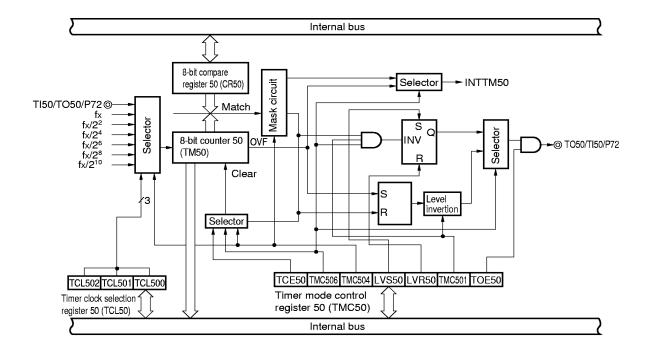

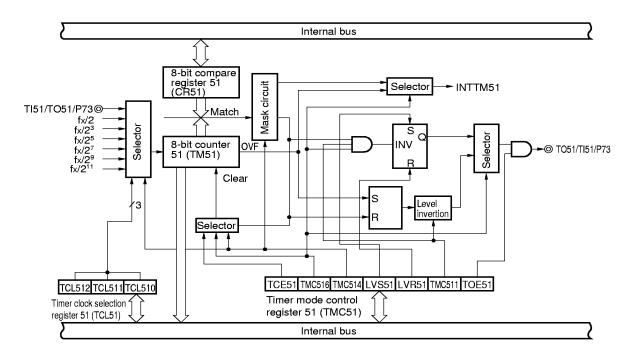

#### 5.3 Timer/Counter

Five timer/counter channels are incorporated.

16-bit timer/event counter: 1 channel

8-bit timer/event counter: 2 channels

Watch timer: 1 channel

Watchdog timer: 1 channel

Table 5-2. Operations of Timer/Event Counter

|     |                         | 16-Bit Timer/<br>Event Counter TM0 | 8-Bit Timer/<br>Event Counter TM50, TM51 | Watch Timer                 | Watchdog Timer              |

|-----|-------------------------|------------------------------------|------------------------------------------|-----------------------------|-----------------------------|

| Оре | eration mode            |                                    |                                          |                             |                             |

|     | Interval timer          | 2 channels <sup>Note 1</sup>       | 2 channels                               | 1 channel <sup>Note 2</sup> | 1 channel <sup>Note 3</sup> |

|     | External event counter  | 1 channel                          | 2 channels                               | _                           | _                           |

| Fur | nction                  |                                    |                                          |                             |                             |

|     | Timer output            | 1 output                           | 2 outputs                                | 1                           | _                           |

|     | PWM output              | _                                  | 2 outputs                                | 1                           | _                           |

|     | Pulse width measurement | 2 inputs                           | _                                        |                             | _                           |

|     | Square wave output      | 1 output                           | 2 outputs                                | 1                           | _                           |

|     | One-shot pulse output   | 1 output                           | _                                        |                             | _                           |

|     | Interrupt source        | 2                                  | 2                                        | 2                           | 1                           |

Notes 1. When capture/compare registers 00, 01 (CR00, CR01) are both specified as compare registers

- 2. The watch timer can perform both watch timer and interval timer functions at the same time.

- 3. The watchdog timer has the watchdog timer and interval timer functions. However, use the watchdog timer by selecting either the watchdog timer function or the interval timer function.

\*

Internal bus ► INTTM00 Noise 16-bit capture/compare elimi-nation register 0 (CR00) TI01/P71@circuit Match fx/2<sup>2</sup> 16-bit timer register fx/26 Clear Output (TMO) -⊚ TO0/TI00/P70 control circuit Noise Match elimination circuit Noise 16-bit capture/compare register 1 (CR01) TI00/TO0/P70@ nation Selector ► INTTM01 Internal bus

Figure 5-2. Block Diagram of 16-bit Timer/Event Counter TM0

Figure 5-3. Block Diagram of 8-bit Timer/Event Counter TM50

Figure 5-4. Block Diagram of 8-bit Timer/Event Counter TM51

Clear fx/2<sup>7</sup> **-**INTWT Selector 9-bit prescaler 5-bit counter fw fw 2<sup>5</sup> fw 2<sup>6</sup>  $\frac{\text{fw}}{2^7}$  $\frac{\text{fw}}{2^4}$ fw 28  $\frac{fw}{2^9}$ Clear Selector -INTWTI WTM7 WTM6 WTM5 WTM4 WTM1 WTM0 0 Watch timer mode control register (WTM) Internal bus

Figure 5-5. Block Diagram of Watch Timer

Figure 5-6. Block Diagram of Watchdog Timer

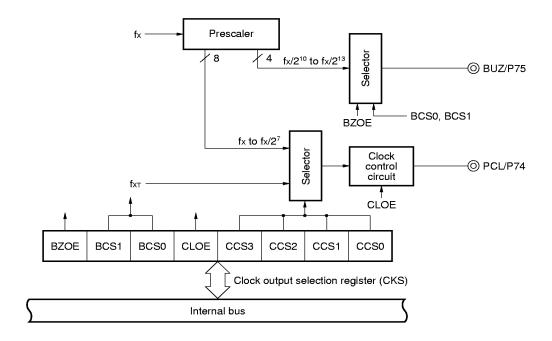

## 5.4 Clock Output/Buzzer Output Control Circuit

A clock output/buzzer output control circuit (CKU) is incorporated.

Clocks with the following variation of frequency can be output as a clock output.

- 65.5 kHz/131 kHz/262 kHz/524 kHz/1.05 MHz/2.10 MHz/4.19 MHz/8.38 MHz (at 8.38-MHz operation with main system clock)

- 32.768 kHz (at 32.768-kHz operation with subsystem clock)

Clocks with the following variation of frequency can be output as a buzzer output.

• 1.02 kHz/2.05 kHz/4.10 kHz/8.19 kHz (at 8.38-MHz operation with main system clock)

## Figure 5-7. Block Diagram of Clock Output/Buzzer Output Control Circuit CKU

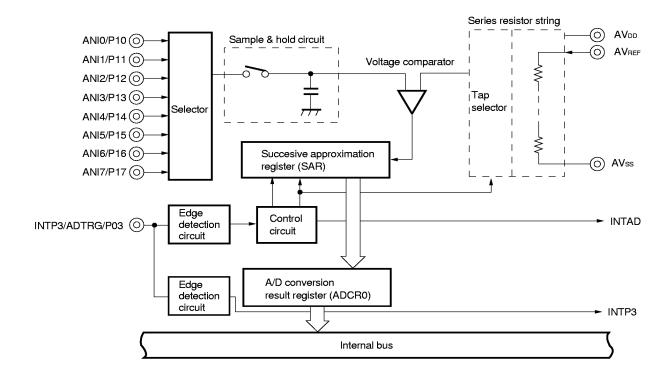

#### 5.5 A/D Converter

An A/D converter of 10-bit resolution  $\times$  8 channels is incorporated.

The following two types of the A/D conversion operation start-up methods are available.

- · Hardware start

- · Software start

Figure 5-8. Block Diagram of A/D Converter

#### 5.6 Serial Interface

Three channels of the serial interface are incorporated.

- Serial interface UART0

- Serial interface SIO30

- · Serial interface IIC0

#### (1) Serial interface UART0

The serial interface UART0 has two modes, asynchronous serial interface (UART) mode and infrared data transfer mode.

#### · Asynchronous serial interface (UART) mode

This mode enables full-duplex operation wherein one byte of data is transmitted and received after the start bit.

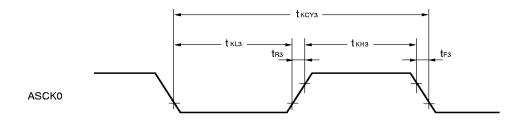

The on-chip dedicated UART baud rate generator enables communication using a wide range of selectable baud rates. In addition, a baud rate can be also defined by dividing the clock input to the ASCK0 pin. The dedicated UART baud rate generator can also be used to generate a MIDI-standard baud rate (31.25 kbps).

#### Infrared data transfer mode

This mode enables pulse output and pulse reception in data format.

This mode can be used for office equipment applications such as personal computers.

Internal bus **ASIMO** Receive buffer RXB0 TXE0 RXE0 PS00 CL0 SL0 ISRMO | IRDAMO registe ASIS0 Transmit shift Receive RxD0/P23 ( PE0 FEO OVEO shift register TxD0/P24 () Receive control control -INTSTO -INTSR0 check - @ P25/ASCK0 Baud rate generator fx/2 to fx/27

Figure 5-9. Block Diagram of Serial Interface UART0

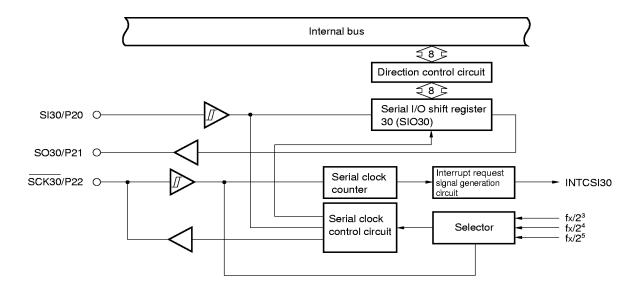

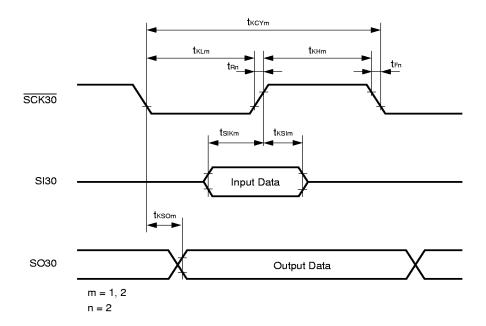

#### (2) Serial interface SIO30

The serial interface SIO30 has the 3-wire serial I/O mode.

#### • 3-wire serial I/O mode (fixed as MSB first)

This is an 8-bit data transfer mode using three lines: serial clock line (SCK30), serial output line (SO30), and serial input line (SI30).

Since simultaneous transmit and receive operations are available in the 3-wire serial I/O mode, the processing time for data transfer is reduced.

The first bit in 8-bit data in the serial transfer is fixed as MSB.

The 3-wire serial I/O mode is useful for connection to a peripheral I/O device that includes a clocked serial interface, a display controller, etc.

Figure 5-10. Block Diagram of Serial Interface SIO30

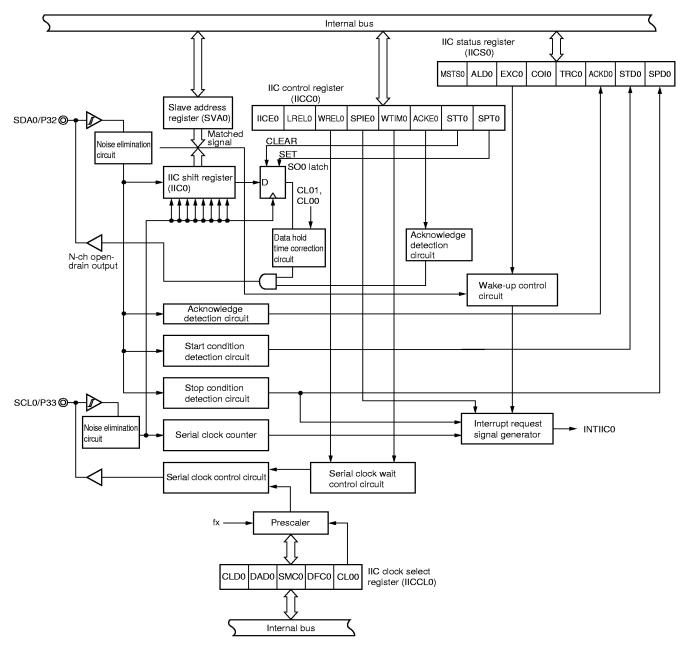

#### (3) Serial interface IIC0

The serial interface IIC0 has the I<sup>2</sup>C (Inter IC) bus mode (multimaster supported).

#### I<sup>2</sup>C bus mode (multimaster supported)

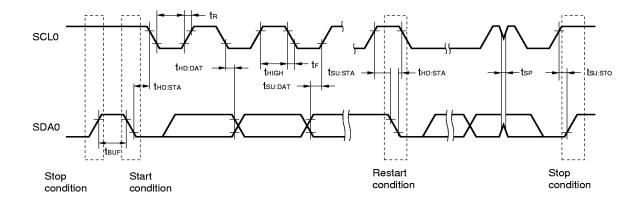

This is an 8-bit data transfer mode using two lines: serial clock line (SCL0) and serial data bus line (SDA0). This mode complies with the I<sup>2</sup>C bus format, and can output "start condition", "data", and stop condition" during transmission via the serial data bus. These data are automatically detected by hardware during reception.

Since the SCL0 and SDA0 are open-drain outputs in IIC0, pull-up resistors for the serial clock line and the serial data bus line are required.

Figure 5-11. Block Diagram of Serial Interface IIC0

## 6. INTERRUPT FUNCTIONS

There are 20 interrupt functions of three different types, as shown below.

Non-maskable: 1Maskable : 18Software : 1

\*

## Table 6-1. Interrupt Source List

| Type of          | Default                    |          | Interrupt Source                                                                                                                              | Internal/ | Vector Table | Basic                                   |

|------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-----------------------------------------|

| Interrupt        | Priority <sup>Note 1</sup> | Name     | Trigger                                                                                                                                       | External  | Address      | Configuration<br>Type <sup>Note 2</sup> |

| Non-<br>maskable | _                          | INTWDT   | Watchdog timer overflow (watchdog timer mode 1 selected)                                                                                      | Internal  | 0004H        | (A)                                     |

| Maskable         | 0                          | INTWDT   | Watchdog timer overflow (interval timer mode selected)                                                                                        |           |              | (B)                                     |

|                  | 1                          | INTP0    | Pin input edge detection                                                                                                                      | External  | 0006H        | (C)                                     |

|                  | 2                          | INTP1    |                                                                                                                                               |           | 0008H        |                                         |

|                  | 3                          | INTP2    |                                                                                                                                               |           | 000AH        |                                         |

|                  | 4                          | INTP3    |                                                                                                                                               |           | 000CH        |                                         |

|                  | 5                          | INTSER0  | Generation of serial interface UART0 reception error                                                                                          | Internal  | 000EH        | (B)                                     |

|                  | 6                          | INTSR0   | End of serial interface UART0 reception                                                                                                       |           | 0010H        |                                         |

|                  | 7                          | INTST0   | End of serial interface UART0 transmission                                                                                                    |           | 0012H        |                                         |

|                  | 8                          | INTCSI30 | End of serial interface SIO3 (SIO30) transfer                                                                                                 |           | 0014H        |                                         |

|                  | 9                          | INTIIC0  | End of serial interface IIC0 transfer                                                                                                         |           | 0018H        |                                         |

|                  | 10                         | INTWTI   | Reference time interval signal from watch timer                                                                                               |           | 001AH        |                                         |

|                  | 11                         | INTTM00  | Generation of coincidence signal of 16-bit timer register and capture/compare register 00 (CR00) (when CR00 is specified as compare register) |           | 001CH        |                                         |

|                  | 12                         | INTTM01  | Generation of coincidence signal of 16-bit timer register and capture/compare register 01 (CR01) (when CR01 is specified as compare register) |           | 001EH        |                                         |

|                  | 13                         | INTTM50  | Generation of coincidence signal of 8-bit timer/event counter 50                                                                              |           | 0020H        |                                         |

|                  | 14                         | INTTM51  | Generation of coincidence signal of 8-bit timer/event counter 51                                                                              |           | 0022H        |                                         |

|                  | 15                         | INTAD0   | End of conversion by A/D converter                                                                                                            |           | 0024H        |                                         |

|                  | 16                         | INTWT    | Watch timer overflow                                                                                                                          |           | 0026H        |                                         |

|                  | 17                         | INTKR    | Falling edge detection of port 4                                                                                                              | External  | 0028H        | (D)                                     |

| Software         | _                          | BRK      | BRK instruction execution                                                                                                                     | _         | 003EH        | (E)                                     |

**Notes 1.** The default priority is a priority order when two or more maskable interrupt requests are generated simultaneously. **0** is the highest order and 17, the lowest.

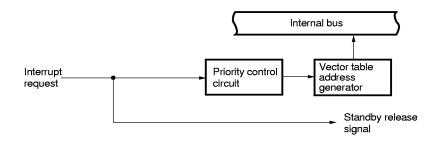

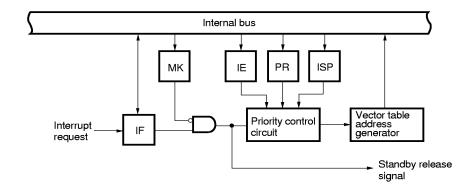

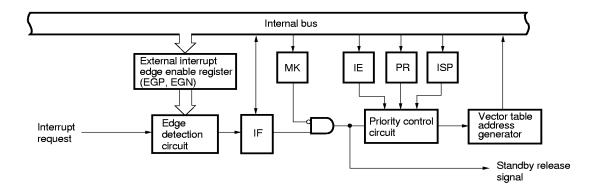

2. Basic configuration types (A) to (E) correspond to (A) to (E) in Figure 6-1, respectively.

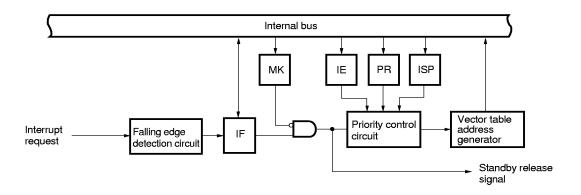

Figure 6-1. Basic Configuration of Interrupt Function (1/2)

## (A) Internal non-maskable interrupt

## (B) Internal maskable interrupt

## (C) External maskable interrupt (INTP0 to INTP3)

Figure 6-1. Basic Configuration of Interrupt Function (2/2)

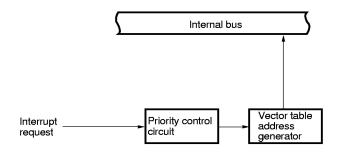

## (D) External maskable interrupt (INTKR)

## (E) Software interrupt

IF : Interrupt request flagIE : Interrupt enable flagISP : In-service priority flagMK : Interrupt mask flag

PR: Priority specification flag

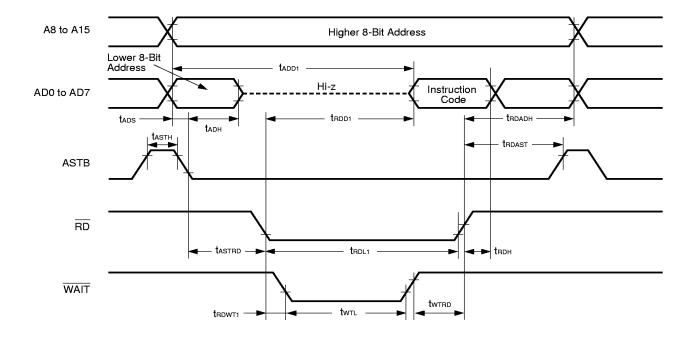

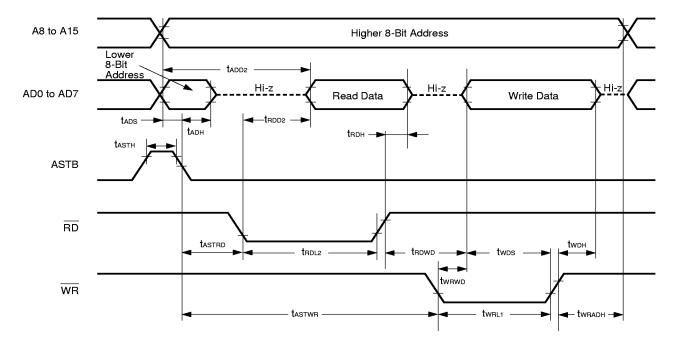

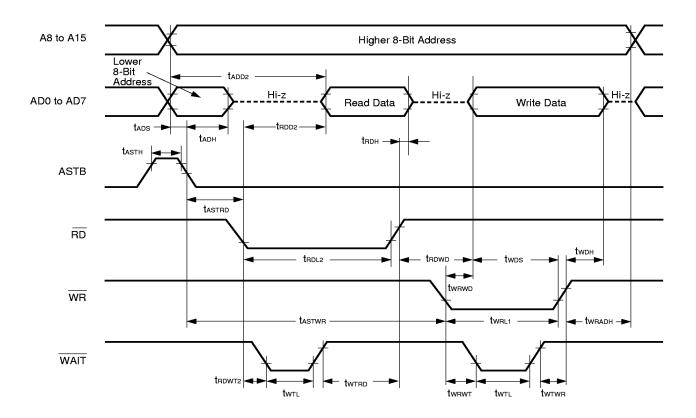

#### 7. EXTERNAL DEVICE EXPANSION FUNCTIONS

The external device expansion functions connect external devices to areas other than the internal ROM, RAM and SFR. Ports 4 to 6 are used for external device connection.

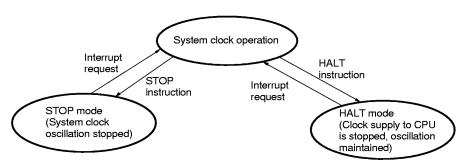

#### 8. STANDBY FUNCTIONS

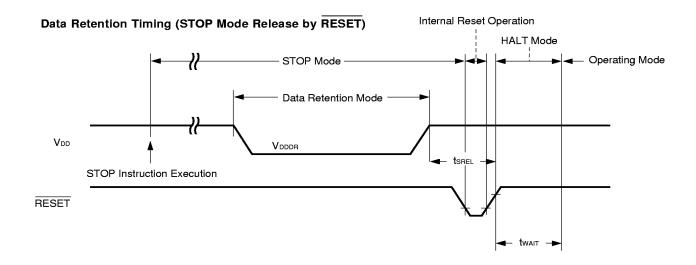

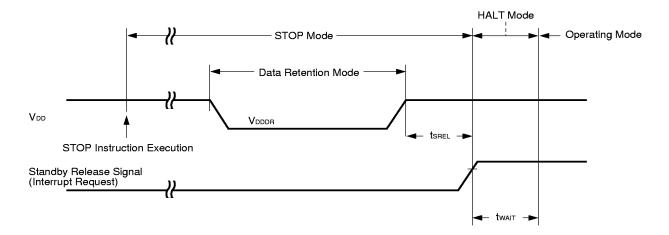

There are the following two standby functions to reduce the consumption current.

- HALT mode: The CPU operating clock is stopped. The average consumption current can be reduced by intermittent operation in combination with the normal operating mode.

- STOP mode: The system clock oscillation is stopped. The whole operation by the system clock is stopped, so that the system operates with ultra-low power consumption.

Figure 8-1. Standby Function

## 9. RESET FUNCTIONS

There are the following two reset methods.

- External reset by RESET pin

- Internal reset by watchdog timer runaway time detection

## 10. INSTRUCTION SET

## (1) 8-bit instructions

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

| Second<br>operand<br>First<br>operand | #byte                                                        | А                                                            | r <sup>Note</sup>                        | sfr        | saddr                                    | !addr16                                  | PSW | [DE]       | [HL]                                     | [HL + byte]<br>[HL + B]<br>[HL + C]      | \$addr16 | 1                          | None         |

|---------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------|------------|------------------------------------------|------------------------------------------|-----|------------|------------------------------------------|------------------------------------------|----------|----------------------------|--------------|

| А                                     | ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP               |                                                              | MOV XCH ADD ADDC SUB SUBC AND OR XOR CMP | MOV<br>XCH | MOV XCH ADD ADDC SUB SUBC AND OR XOR CMP | MOV XCH ADD ADDC SUB SUBC AND OR XOR CMP | MOV | MOV<br>XCH | MOV XCH ADD ADDC SUB SUBC AND OR XOR CMP | MOV XCH ADD ADDC SUB SUBC AND OR XOR CMP |          | ROR<br>ROL<br>RORC<br>ROLC |              |

| r                                     | MOV                                                          | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            | INC<br>DEC   |

| B, C                                  |                                                              |                                                              |                                          |            |                                          |                                          |     |            |                                          |                                          | DBNZ     |                            |              |

| sfr                                   | MOV                                                          | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            |              |

| saddr                                 | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          | DBNZ     |                            | INC<br>DEC   |

| !addr16                               |                                                              | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            |              |

| PSW                                   | MOV                                                          | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            | PUSH<br>POP  |

| [DE]                                  |                                                              | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            |              |

| [HL]                                  |                                                              | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            | ROR4<br>ROL4 |

| [HL + byte]<br>[HL + B]<br>[HL + C]   |                                                              | MOV                                                          |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            |              |

| Х                                     |                                                              |                                                              |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            | MULU         |

| С                                     |                                                              |                                                              |                                          |            |                                          |                                          |     |            |                                          |                                          |          |                            | DIVUW        |

Note Except r = A

## (2) 16-bit instructions

MOVW, XCHW, ADDW, SUBW, CMPW, PUSH, POP, INCW, DECW

| Second operand First operand | #word                | AX                   | rp <sup>Note</sup> | sfrp | saddrp | !addr16 | SP   | None                    |

|------------------------------|----------------------|----------------------|--------------------|------|--------|---------|------|-------------------------|

| AX                           | ADDW<br>SUBW<br>CMPW |                      | MOVW<br>XCHW       | MOVW | MOVW   | MOVW    | MOVW |                         |

| rp                           | MOVW                 | MOVW <sup>Note</sup> |                    |      |        |         |      | INCW, DECW<br>PUSH, POP |

| sfrp                         | MOVW                 | MOVW                 |                    |      |        |         |      |                         |

| saddrp                       | MOVW                 | MOVW                 |                    |      |        |         |      |                         |

| !addr16                      |                      | MOVW                 |                    |      |        |         |      |                         |

| SP                           | MOVW                 | MOVW                 |                    |      |        |         |      |                         |

Note Only when rp = BC, DE or HL

#### (3) Bit manipulation instructions

MOV1, AND1, OR1, XOR1, SET1, CLR1, NOT1, BT, BF, BTCLR

| Second operand First operand | A.bit                       | sfr.bit                     | saddr.bit                   | PSW.bit                     | [HL].bit                    | CY   | \$addr16          | None                 |